Главный производитель чипов переходит на 5 нм и уводит разработку в облака

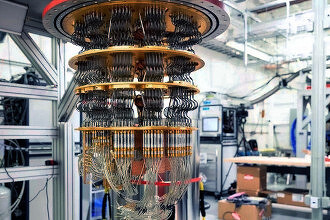

Крупнейший в мире контрактный производитель полупроводников уходит в технологический и производственный отрыв. Пробное производство чипов с литографией EUV и нормами 5 нм стартует в апреле 2019 г., разработка чипов постепенно переносится в облака.Эпоха производства полупроводников с нормами 5 нм началась

Компания Taiwan Semiconductor Manufacturing Company (TSMC), крупнейший в мире контрактный производитель полупроводников, объявила о выпуске первых чипов с частичным применением нового технологического процесса на базе литографии так называемого глубокого ультрафиолетового спектра (Extreme Ultraviolet Lithography, EUV).

Одновременно компания анонсировала планы по выпуску первых чипов по техпроцессу N5 с нормами 5 нм и полным переходом на EUV-литографию уже в апреле 2019 г. В дополнение, TSMC также огласила список из первых четырех компаний, выступивших партнерами в развитии онлайн-сервисов для облачной разработки полупроводниковых микросхем.

По данным компании, для производства с применением техпроцесса N5 уже сегодня готов ряд базовых модулей и узлов, однако некоторые инструменты для автоматической разработки чипов (Electronic design automation, EDA) достигнут стадии готовности уровня 0.9 не ранее ноября 2018 г., а некоторые модули, включая разводку шин PCIe Gen 4, USB 3.1 и др., будут готовы к использованию с техпроцессом N5 только к июню 2019 г.

Разрыв между лидерами резко увеличивается

В настоящее время, по словам представителей TSMC, компания запустила в опытное производство первую контрактную микросхему с нормами обновленного техпроцесса N7+, который отличается от базового использованием EUV-литографии для разводки до четырех уровней кристалла. По данным компании, при переходе к техпроцессу N5 литография EUV будет использоваться для разводки до 14 уровней чипа.

Переход к использованию фотолитографии глубокого ультрафиолета (свет с длиной волны около 13,5 нм) вместо нынешних иммерсионных аргон-фторидных систем (193 нм) позволит значительно сэкономить на уменьшении числа фотомасок (в нынешних техпроцессах применяется набор масок для увеличения точности посредством фазового сдвига).

По данным EE Times, один из ближайших конкурентов TSMC, южнокорейская Samsung, также намерена использовать фотолитографию EUV на производственных линиях с нормами 7 нм. Переход Intel на фотолитографию EUV в ближайшее время не ожидается вовсе, а Globalfoundries объявила в августе 2018 г. о полной заморозке работ по развертыванию линий 7 нм, с EUV и без.

Представители TSMC заявили, что компания уже провела экспериментальный выпуск пробных партий процессорных ядер ARM A72 с техпроцессом N5. Тестирование показало, что переход на нормы 5 нм обеспечивает прирост производительности чипов на 14,7-17,7%, при этом площадь кристалла по сравнению с техпроцессом 7 нм уменьшается в 1,8-1,86 раз. Для улучшенного техпроцесса N7+ в компании отмечают снижение энергопотребления чипа на 6-12% и уменьшение площади кристалла на 20%. Данных о разнице в производительности между чипами с нормами N7 и N7+ в компании не приводят, однако Клифф Хоу (Cliff Hou), вице-президент TSMC по технологиям разработки, заявил, что N7+ обеспечит «сравнимую с N7 аналоговую производительность».

По данным компании, инструментарий для автоматической разработки чипов под техпроцесс N7+ также будет готов к апрелю 2019 г. По данным TSMC, плотность размещения транзисторов при производстве с техпроцессом N7 в 16,8 раз выше, нежели с нормами 40 нм.

По информации источников EE Times, суммарная стоимость разработки и запуска в производство чипов по техпроцессу N5, включая дизайн и лицензирование, будет достигать $200-$250 млн, что значительно выше типичных $150 млн для норм 7 нм.

Разработка новейших полупроводников уходит в облака

TSMC также объявила о начале сотрудничества с Amazon Web Services, Cadence, Microsoft Azure и Synopsys на предмет развертывания облачных сервисов разработки полупроводниковых чипов.

Изначально сервис под названием Virtual Design Environment (виртуальная среда разработки) будут использовать базовые модули Cadence и Synopsys для создания типичных регистрово-межуровневых цифровых цепей RTL-GDSII, а также пользовательских межуровневых GDSII-цепей.

На перспективу в TSMC надеются, что со временем другие производители средств автоматической разработки чипов подтянутся со своими новыми разработками, в том числе, для цепей front-end. Тестирование сервиса производилось на дизайне статической памяти с нормами 5 нм (N5 SRAM). Помимо этого, Synopsys также использовала сервис для разводки блока физического уровня шины PCIe Gen 5 для техпроцесса TSMC с нормами 7 нм, а стартап SiFive применил его для разводки вычислительного ядра RISC-V с нормами 28 нм.

Для запуска сервиса Virtual Design Environment заказчик должен связаться с одним из партнеров TSMC. Далее в рамках техзадания создается специальный сайт, по умолчанию учитывающий все требования проекта и лицензионные соглашения. Так, объединенная команда выше упомянутого стартапа SiFive с офисами в Кремниевой Долине, Калифорния, и Бангалоре, Индия, с помощью единого облачного сервиса смогла завершить разработку своего чипа в рекордные сроки – менее чем за три месяца.

Поделиться

Поделиться